#### NetTAG: A Multimodal RTL-and-Layout-Aligned Netlist Foundation Model via Text-Attributed Graph

Wenji Fang<sup>1</sup>, Wenkai Li<sup>1</sup>, Shang Liu<sup>1</sup>, Yao Lu<sup>1</sup>, Hongce Zhang<sup>2</sup>, Zhiyao Xie<sup>1</sup>

<sup>1</sup> Hong Kong University of Science and Technology <sup>2</sup>Hong Kong University of Science and Technology (Guangzhou)

SPONSORED BY

#### **Circuit Foundation Model**

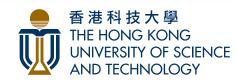

### **From Task-Specific to Circuit Foundation Model**

- Traditional: task-specific supervised predictive AI for EDA

- Tedious, time-consuming, not generalized

- New trend<sup>1</sup>: general self-supervised Circuit Foundation Model

- Encode circuit into general embeddings for various EDA tasks (circuit encoder)

- *Pre-training* to capture circuit intrinsics (self-supervised)

- *Fine-tuning* for EDA tasks (supervised)

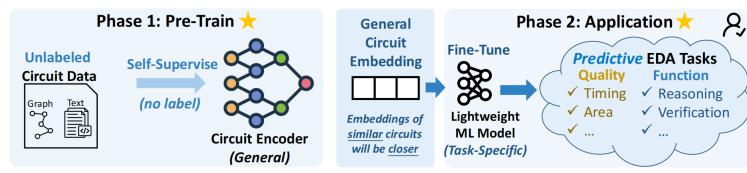

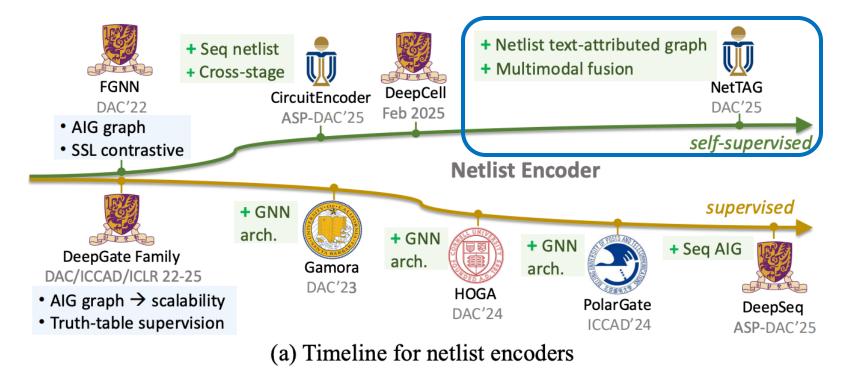

### **Circuit Representation Learning (Encoders)**

• Netlist encoder: most actively explored

<sup>1</sup>Wenji Fang et al. A Survey of Circuit Foundation Model: Foundation AI Models for VLSI Circuit Design and EDA

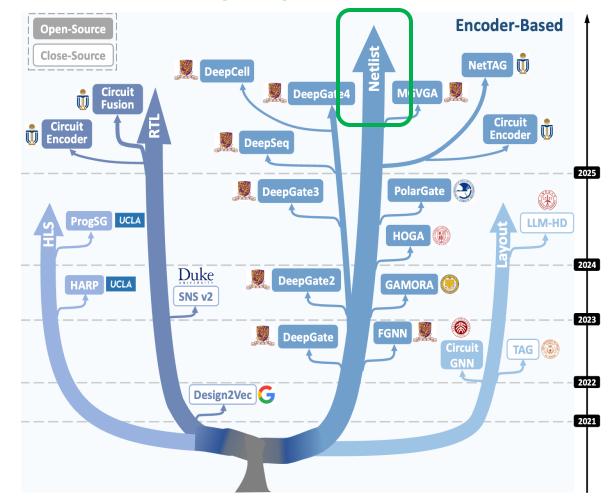

### **Existing Netlist (AIG) Encoders**

- Limitation: graph-only, only supports AIG

- Graph structure over functionality

- Limited to AIG, post-syn netlists?

- Rely on functional supervision (e.g., truth table)

- Lack of physical encoding, PPA tasks?

- How about LLM?

- Textual semantics rather than structure

- Struggle with netlists (low-level, bit-blasted)

- Lack of structural encoding

### **Motivation: LLM + Graph**

- Limitation: graph-only, only supports AIG

- Graph structure over functionality

- Limited to AIG, post-syn netlists?

- Rely on fu Can we fuse them together?

- LLM (Semantic) + Graph (Structure)

- **Multimodal Fusion on Netlist!**

- Textual semantics father than structure

- Struggle with netlists (low-level, bit-blasted)

- Lack of structural encoding

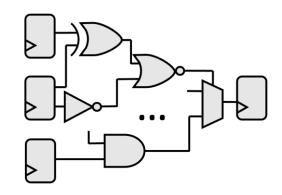

### **Multimodal Fusion on Circuit: RTL vs Netlist**

- Multimodal learning: fuse information from diverse modalities

- Vision-language

۰

. . . . . .

- Multimodal learning on RTL<sup>2</sup>

- Register-transfer level (RTL)

- *Earlier* stage → more *semantic*

- Fuse 3 RTL modalities at *register level*

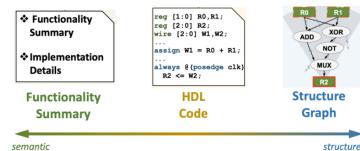

- Multimodal learning on netlist?

- Gate-level netlists

- Later stage → more structure

- Should fuse at gate level

<sup>2</sup>Wenji Fang et al. CircuitFusion: Multimodal Circuit Representation Learning for Agile Chip Design. [ICLR'25]

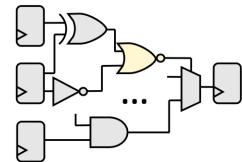

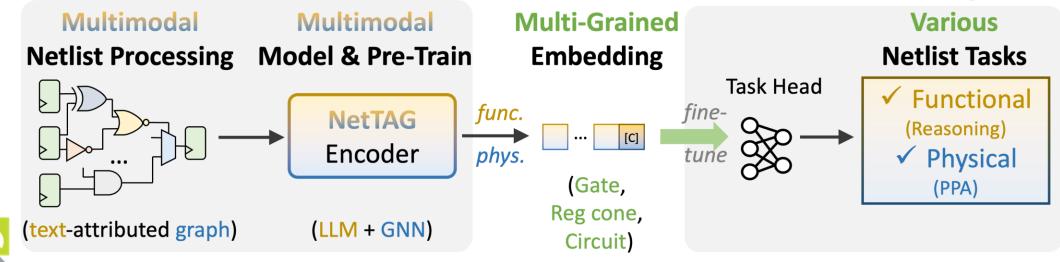

# NetTAG: Multimodal Netlist Foundation Model

- Overview

#### **NetTAG: A General Netlist Foundation Model**

#### • Goal: develop a general netlist encoder

- Pre-train: netlist → embeddings w. functional and physical information

- Fine-tune: support various EDA tasks w. the embedding

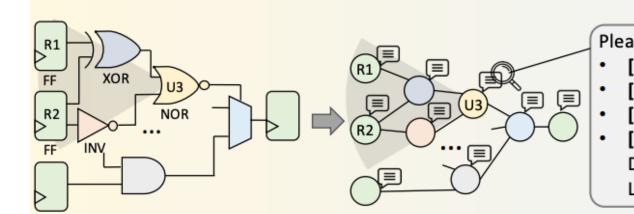

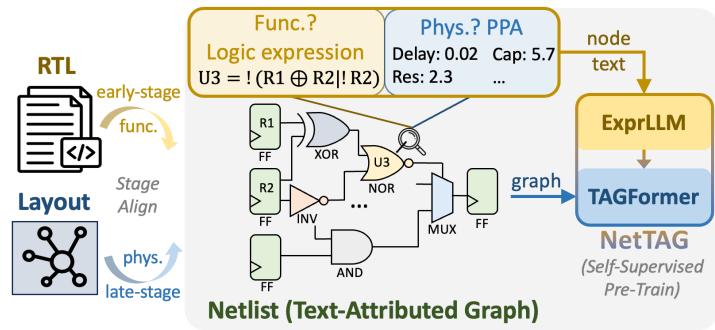

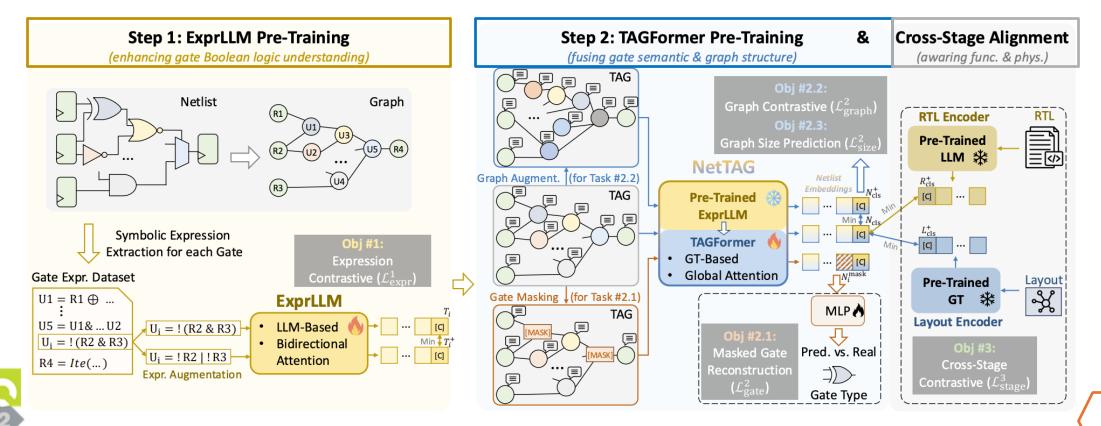

### NetTAG: Multimodal Netlist Encoder via TAG

- Key idea: fuse local gate text with global structure graph

- Multimodal preprocess: netlist → text-attributed graph

- Multimodal 2-stage model: *gate text* (LLM) + *circuit graph* (GNN)

- Multimodal pre-train: self-supervised & cross-stage-aware

#### **Pre-Training**

#### **Fine-Tuning**

### **NetTAG: Moving From AIG-Only to Any Netlist**

- Key advantages: first post-syn netlist encoder w. both func. & phys.

- Support diverse gate types (any netlist gate)

- Support multiple circuit granularities (gate & register & circuit)

- Support various netlist tasks (func. & phys.)

## NetTAG: Multimodal Netlist Foundation Model

- Implementation Details

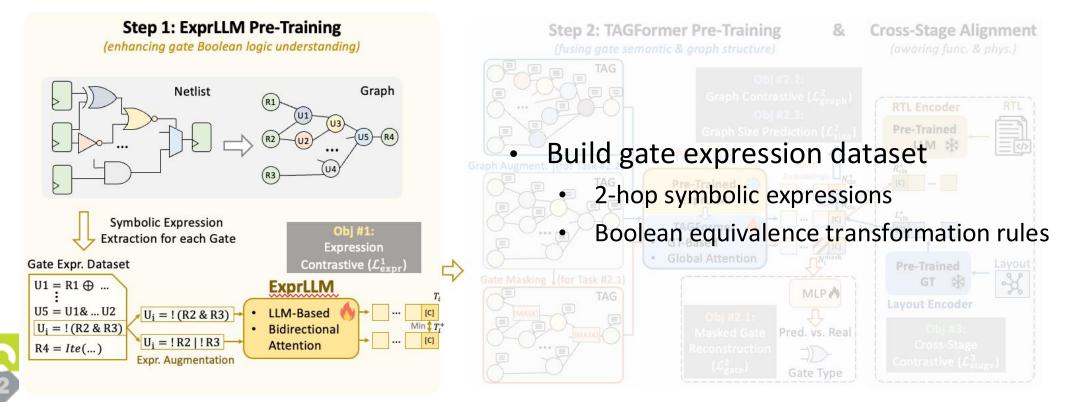

#### **Preprocessing: Netlist as TAG**

- Text-attributed graph: 1. node (gate) text attribute + 2. graph connectivity

- **1. Gate**  $\rightarrow$  **text:** local functional & physical info  $\rightarrow$  *semantics*

- Functional: gate symbolic logic expression

- E.g., U3 = ! ((R1 ⊕ R2) | ! R2)

- Physical: gate physical characteristic vector

- Advantages: various gate types & structure independence & LLM compatible

- Circuit → graph: global connectivity → structure

#### Node Text Attribute Example

Please analyze this netlist gate:

- [Name] U3

- [Type] NOR

- [Symbolic expression] U3 = !(R1 ⊕ R2 | !R2)

- [Physical property] {Power: 3.3, Area: 1.1, Delay: 0.02, Toggle Rate: 0.8, Probability: 0.5, Load: 0.2, Capacitance: 5.7, Resistance: 2.3}

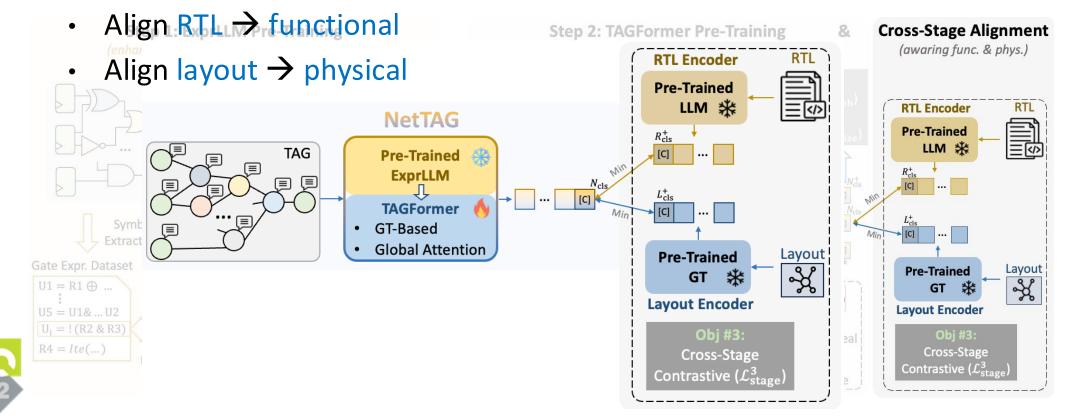

### Model: NetTAG Multimodal Architecture

- NetTAG two-stage encoding for netlist TAG

- S1. ExprLLM (LLM encoder): Gate-level text → node local initialization

- S2. TAGFormer (GT): Circuit-level graph → graph global refinement

- Auxiliary RTL and layout encoders → Cross-stage align<sup>3</sup>

#### Pre-Train: Multimodal Self-Supervised (Overview)

- Goal: enhance netlist *functional* and *physical* awareness

- Two-stage encoding → Two-step pre-training + Cross-stage alignment

#### Pre-Train: Multimodal Self-Supervised (Text)

- Step 1: Enhancing logic understanding in ExprLLM

- **Goal 1:** Differentiate gate expression text functionality

- **Objective # 1:** Symbolic expression text contrastive learning

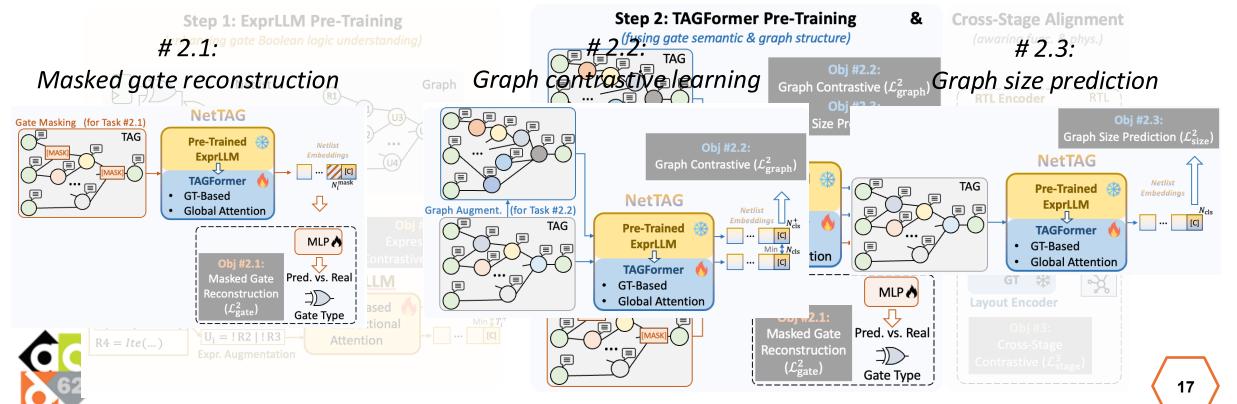

### Pre-Train: Multimodal Self-Supervised (Graph)

#### • Step 2: Fusion in TAGFormer

- Goal 2: Training within TAGFormer for semantic and structure fusion

- **Objective # 2:** Node & graph-level self-supervised

#### Pre-Train: Multimodal Self-Supervised (Stage)

#### • Step 3: Cross-stage alignment

- Goal 3: Training beyond NetTAG for cross-stage func. & phys. awareness

- **Objective # 3:** Cross-stage contrastive alignment

#### **Experimental Results**

### **Support Largely Different EDA Tasks – Functional**

#### • Functional tasks: reasoning earlier RTL function (classification)

- Task 1: Comb. gate function<sup>4</sup>

- Node-level

|        | <b>GNN-RE</b> [14] |       |        |            | NetTAG |       |        |     |

|--------|--------------------|-------|--------|------------|--------|-------|--------|-----|

| Design | Acc.               | Prec. | Recall | <b>F</b> 1 | Acc.   | Prec. | Recall | F1  |

|        | (%)                | (%)   | (%)    | (%)        | (%)    | (%)   | (%)    | (%) |

| 1      | 79                 | 82    | 79     | 74         | 97     | 97    | 97     | 97  |

| 2      | 96                 | 96    | 96     | 96         | 100    | 100   | 100    | 100 |

| 3      | 94                 | 94    | 94     | 94         | 100    | 100   | 100    | 100 |

| 4      | 78                 | 83    | 78     | 78         | 100    | 100   | 100    | 100 |

| 5      | 91                 | 92    | 91     | 90         | 99     | 99    | 99     | 99  |

| 6      | 74                 | 78    | 74     | 68         | 94     | 94    | 94     | 93  |

| 7      | 80                 | 80    | 80     | 80         | 84     | 87    | 84     | 81  |

| 8      | 89                 | 90    | 89     | 87         | 95     | 96    | 95     | 96  |

| 9      | 65                 | 77    | 65     | 67         | 100    | 100   | 100    | 100 |

| Avg.   | 83                 | 86    | 83     | 82         | 97     | 97    | 97     | 96  |

<sup>4</sup>Lilas Alrahis et al. GNN-RE Graph Neural Networks for Reverse Engineering of Gate-Level Netlists. [TCAD'22] • Task 2: Seq. state/data register<sup>5</sup>

|            | Task 2 |         |        |      |  |  |  |

|------------|--------|---------|--------|------|--|--|--|

| Design     | REIGN  | NN [15] | NetTAG |      |  |  |  |

| Design     | Sens.  | Acc.    | Sens.  | Acc. |  |  |  |

|            | (%)    | (%)     | (%)    | (%)  |  |  |  |

| itc1       | 50     | 72      | 100    | 98   |  |  |  |

| itc2       | 100    | 92      | 100    | 100  |  |  |  |

| chipyard1  | 30     | 65      | 80     | 79   |  |  |  |

| chipyard2  | 30     | 65      | 90     | 86   |  |  |  |

| vex1       | 50     | 74      | 82     | 74   |  |  |  |

| vex2       | 32     | 60      | 86     | 82   |  |  |  |

| opencores1 | 42     | 73      | 93     | 84   |  |  |  |

| opencores2 | 37     | 80      | 92     | 82   |  |  |  |

| Avg.       | 46     | 73      | 90     | 86   |  |  |  |

Subgraph-level

<sup>5</sup>Subhajit et al. ReIGNN: State Register Identification Using Graph Neural Networks for Circuit Reverse Engineering. [ICCAD'21]

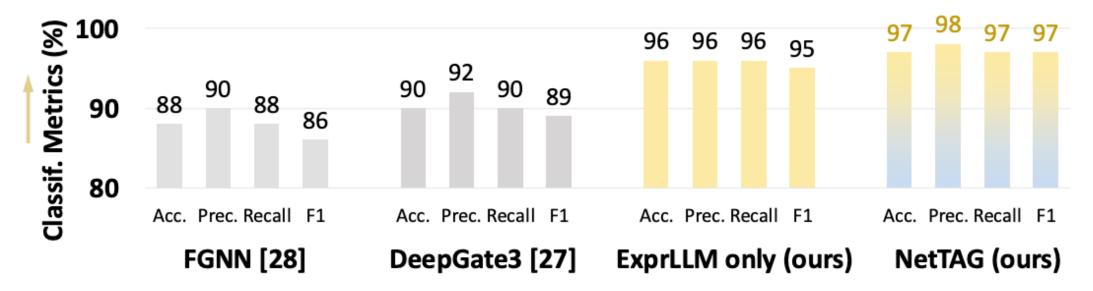

#### **Comparison with AIG Functional Encoders**

- Existing netlist encoders<sup>6,7</sup> only support AIG format

- AIG version of Task 1

- ExprLLM-only can already achieve high accuracy

<sup>6</sup>Ziyi Wang et al. Functionality Matters in Netlist Representation Learning. [DAC'22] <sup>7</sup>Zhengyuan Shi et al. DeepGate3: Towards Scalable Circuit Representation Learning. [ICCAD'22]

#### Support Largely Different EDA Tasks – Physical

- Physical tasks: predicting later layout PPA (regression)

- Task 3: Register slack

- Subgraph-level

|            | Task 3 |       |        |      |  |  |  |

|------------|--------|-------|--------|------|--|--|--|

| Design     | G      | NN* [ | NetTAG |      |  |  |  |

| Design     | R      | MAPE  | R      | MAPE |  |  |  |

|            |        | (%)   |        | (%)  |  |  |  |

| itc1       | 0.89   | 13    | 0.94   | 9    |  |  |  |

| itc2       | 0.91   | 10    | 0.93   | 9    |  |  |  |

| chipyard1  | 0.72   | 17    | 0.7    | 20   |  |  |  |

| chipyard2  | 0.86   | 12    | 0.95   | 9    |  |  |  |

| vex1       | 0.94   | 11    | 0.93   | 12   |  |  |  |

| vex2       | 0.97   | 18    | 0.97   | 9    |  |  |  |

| opencores1 | 0.99   | 26    | 0.92   | 29   |  |  |  |

| opencores2 | 0.93   | 30    | 0.98   | 26   |  |  |  |

| Avg.       | 0.9    | 17    | 0.92   | 15   |  |  |  |

- Task 4: Design power/area

- Graph-level

| Target Metric <sup>†</sup> |         | EDA Tool |      | GNN* |      | NetTAG |      |

|----------------------------|---------|----------|------|------|------|--------|------|

|                            |         | R        | MAPE | R    | MAPE | R      | MAPE |

|                            |         |          | (%)  |      | (%)  |        | (%)  |

| <b>A</b> #20               | w/o opt | 0.99     | 5    | 0.99 | 5    | 0.99   | 4    |

| Area                       | w/ opt  | 0.95     | 34   | 0.95 | 18   | 0.96   | 11   |

| Down                       | w/o opt | 0.99     | 34   | 0.99 | 12   | 0.99   | 8    |

| Power                      | w/ opt  | 0.73     | 38   | 0.76 | 19   | 0.86   | 12   |

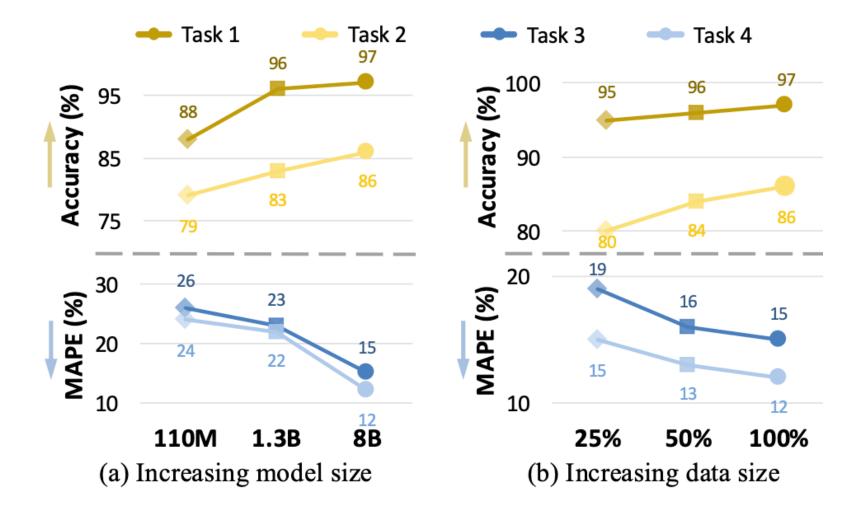

#### **Observation on Foundation Model Scaling Law**

• Scalability: performance scaling up w. model/data size

### **Conclusion and Future Work**

- NetTAG: first multimodal netlist encoder for any post-syn netlists

- Insight: graph-only → multimodal fusion paradigm via TAG

- Future work<sup>8</sup>

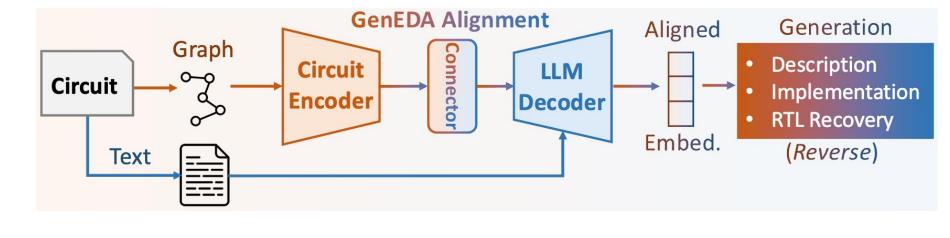

- Bridging the gap between Circuit Encoder and LLM Decoder

- Integrate NetTAG into LLMs for generative netlist function reasoning

Code

Paper

#### **Backup: Experimental Setup**

#### Dataset and preparation

- Dataset statistics: 626k expression & 200k netlist subcircuits & 10k aligned RTL/layout

- Symbolic logic expression manipulation: PySMT

- Model Implementation

- ExprLLM: LLM2Vec, an LLM encoder w. bidirectional attention (max 8k input)

- TAGFormer: SGFormer, a graph transformer

- RTL encoder: NV-Embed (max 32k input)

- Layout encoder: another SGFormer

|           | Gate E                    | xpression | Circuit Netlist |                   |  |

|-----------|---------------------------|-----------|-----------------|-------------------|--|

| Source    | # Data # Tokens<br>(Avg.) |           | # Data          | # Nodes<br>(Avg.) |  |

| ITC99     | 47k                       | 6,960     | 4k              | 1,025             |  |

| OpenCores | 76k                       | 212       | 55k             | 173               |  |

| Ĉhipyard  | 109k                      | 9,849     | 20k             | 2,813             |  |

| VexRiscv  | 81k                       | 5,289     | 21k             | 901               |  |

| Total     | 313k                      | 5,810     | 100k            | 855               |  |

TABLE II: Statistics of circuit expression and netlist dataset.

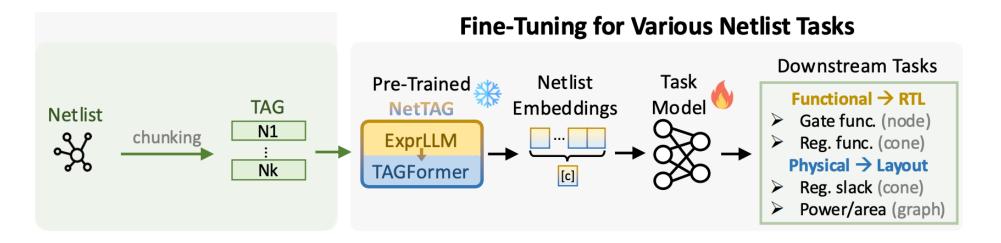

### **Backup: Fine-Tuning for Various Netlist Tasks**

- Fine-tune embeddings with lightweight task models

- Reasoning earlier RTL function

- Predicting later layout PPA

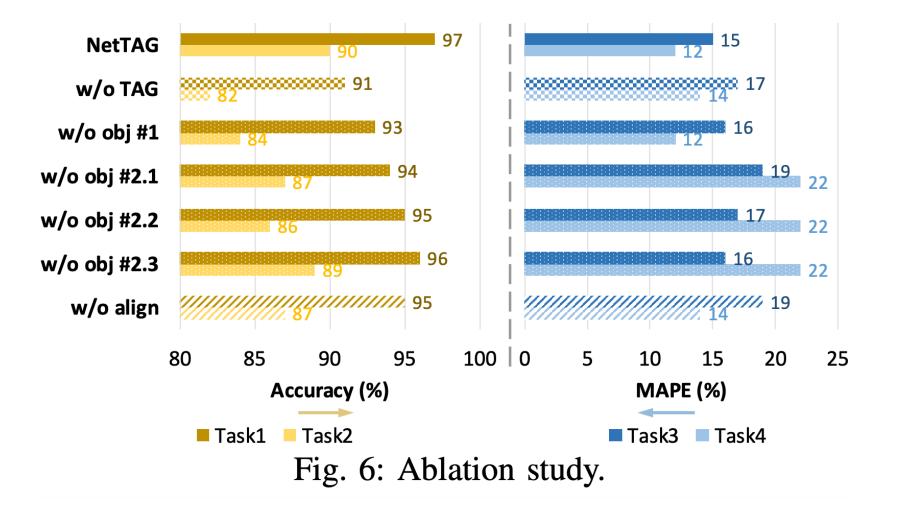

#### **Backup: Ablation Study**

### **Backup: Runtime Analysis**

- 10x speedup over physical design process

- Key runtime factor

- Symbolic expression extraction

- Improve: gate-level parallelism

- ExprLLM inference

- Improve: more GPU resources

|           | EDA Tool |      |         |           |       |

|-----------|----------|------|---------|-----------|-------|

| Source    | P&R      | Pre* | l II    | Total     |       |

|           | (Avg.)   | rie  | ExprLLM | TAGFormer | 10121 |

| ITC99     | 164      | 2    | 5       | 0         | 7     |

| OpenCores | 288      | 18   | 12      | 1         | 31    |

| Ĉhipyard  | 251      | 15   | 10      | 1         | 26    |

| VexRiscv  | 207      | 8    | 5       | 2         | 15    |

| GNNRE     | /        | 4    | 2       | 0         | 6     |

TABLE VI: Runtime (minutes) Comparision.

\* Preprocessing (chunking into cones and converting netlist into TAG).