# DAC Young Fellows

## NetTAG: A Multimodal RTL-and-Layout-Aligned Netlist Foundation Model via Text-Attributed Graph

Wenji Fang, Wenkai Li, Shang Liu, Yao Lu, Hongce Zhang, Zhiyao Xie Hong Kong University of Science and Technology

### Background: Circuit Foundation Model ☐ Paradigm Shift of Al for EDA - Widely adopted: task-specific supervised learning - New trend: general self-supervised Circuit Foundation Model Phase 1: Pre-Train (b) Type II: General Encoder-Based Circuit Foundation Model Paradigm ☐ Netlist Representation Learning (Encoder) - Most actively explored type of circuit encoders - Limitation: graph-only for AIG - Structure over function self-supervised **Netlist Encoder** - Need functional supervision

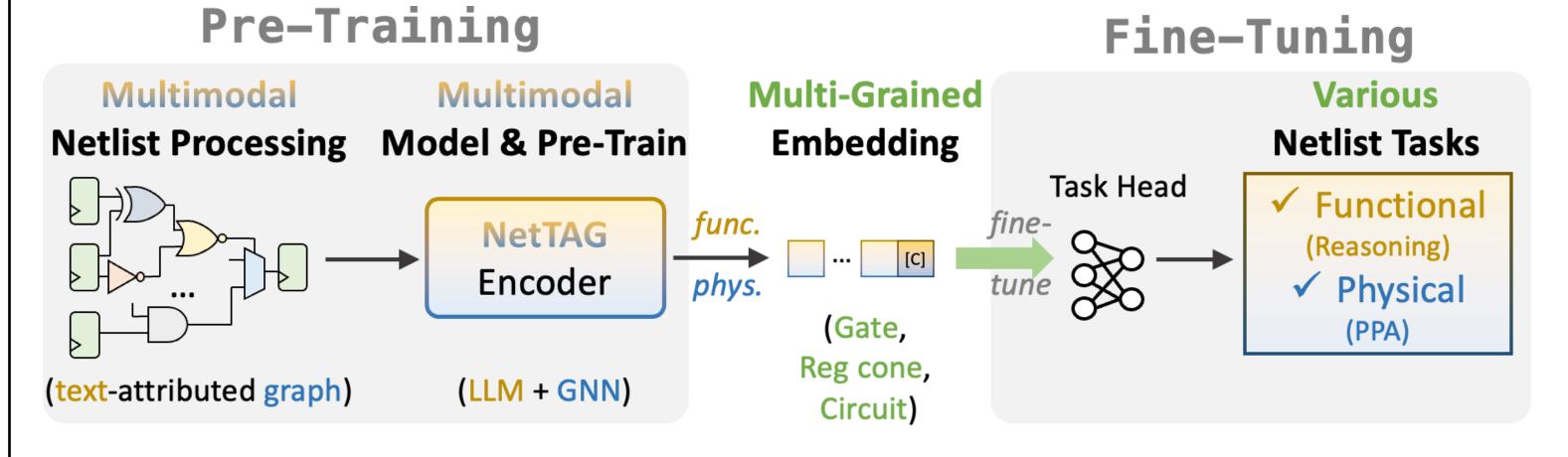

#### Method: Multimodal Netlist Encoder

**U NetTAG Overview**

- No physical encoding, PPA?

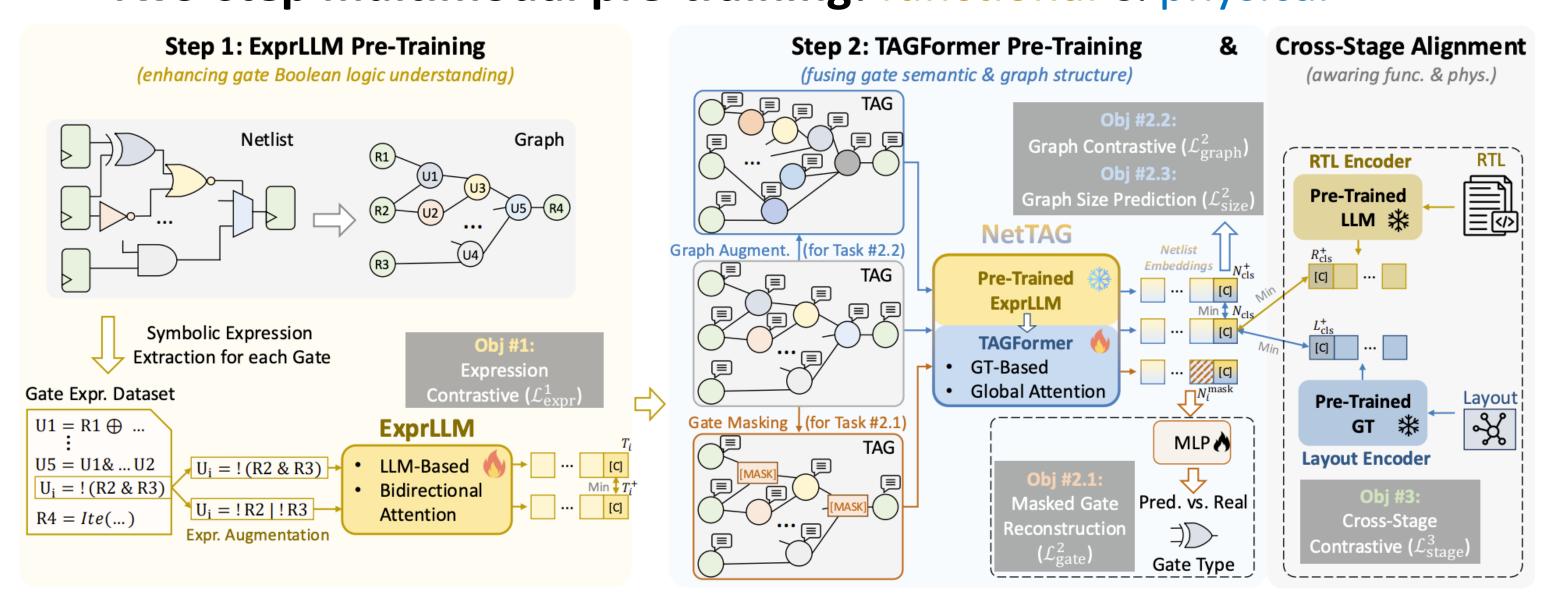

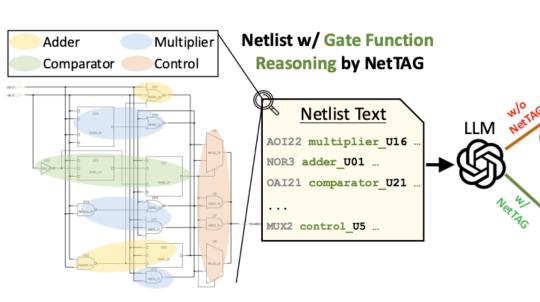

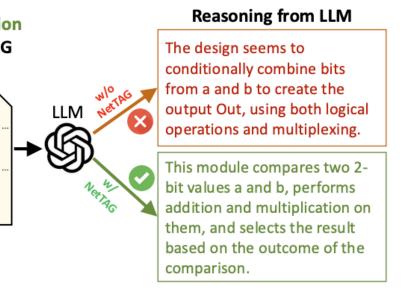

- Key idea: fuse local gate text with global structure graph via TAG

- Key advantages:

- Any gate type & multi circuit granularities & func. + phys. tasks

- Key steps: netlist preprocess → pre-training → fine-tuning

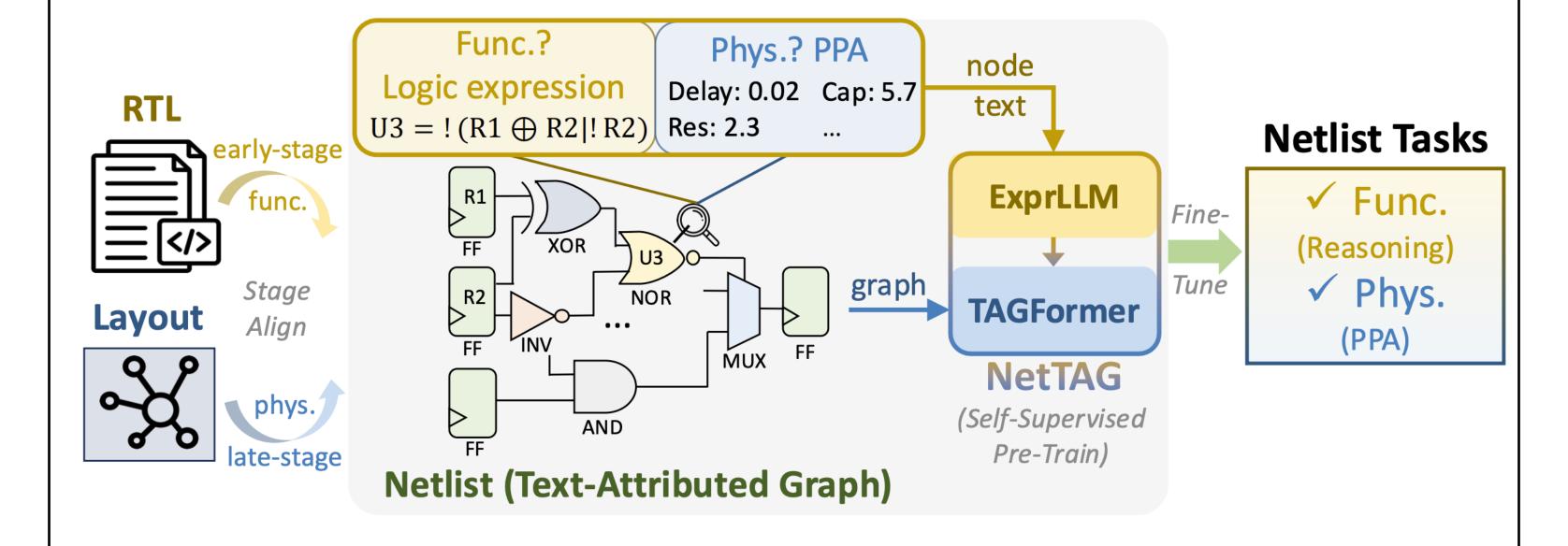

### ☐ Process: Netlist as Text-Attributed Graph

- TAG: gate text semantics (local) + circuit graph structure (global)

- Functional: gate symbolic logic expression

- Physical: gate physical characteristic vector

- Advantages:

- Various gate types &structure independence &LLM compatible

### ☐ Model: Multimodal Encode & Pre-train - Two-phase netlist encoding: gate text (LLM) + circuit graph (GT)

- Two-step multimodal pre-training: functional & physical

### **Experimental Results**

#### ☐ Support Various Largely Different EDA Tasks

- Functional tasks: reasoning earlier RTL function (classification)

- √ Task 1: Comb. gate function

√ Task 2: Seq. state/data register

- Gate-level

| F1  |

|-----|

| (%) |

| 97  |

| 100 |

| 100 |

| 100 |

| 99  |

| 93  |

|           | Task 2 |         |        |      |  |

|-----------|--------|---------|--------|------|--|

| Design    | REIGN  | NN [15] | NetTAG |      |  |

| Design    | Sens.  | Acc.    | Sens.  | Acc. |  |

|           | (%)    | (%)     | (%)    | (%)  |  |

| itc1      | 50     | 72      | 100    | 98   |  |

| itc2      | 100    | 92      | 100    | 100  |  |

| chipyard1 | 30     | 65      | 80     | 79   |  |

| chipyard2 | 30     | 65      | 90     | 86   |  |

| vex1      | 50     | 74      | 82     | 74   |  |

| *****     | 22     | 60      | 06     | 92   |  |

- Subgraph-level

- Physical tasks: predicting later layout PPA (regression)

- ✓ Task 3: Register slack

- Subgraph-level

|            | Task 3 |      |        |      |  |  |

|------------|--------|------|--------|------|--|--|

| Design     | G      | NN*  | NetTAG |      |  |  |

| Design     | R      | MAPE | R      | MAPE |  |  |

|            |        | (%)  |        | (%)  |  |  |

| itc1       | 0.89   | 13   | 0.94   | 9    |  |  |

| itc2       | 0.91   | 10   | 0.93   | 9    |  |  |

| chipyard1  | 0.72   | 17   | 0.7    | 20   |  |  |

| chipyard2  | 0.86   | 12   | 0.95   | 9    |  |  |

| vex1       | 0.94   | 11   | 0.93   | 12   |  |  |

| vex2       | 0.97   | 18   | 0.97   | 9    |  |  |

| opencores1 | 0.99   | 26   | 0.92   | 29   |  |  |

| opencores2 | 0.93   | 30   | 0.98   | 26   |  |  |

| Avg.       | 0.9    | 17   | 0.92   | 15   |  |  |

✓ Task 4: Design power/area

| Target Metric <sup>†</sup> |         | EDA Tool |      | GNN* |      | NetTAG |      |

|----------------------------|---------|----------|------|------|------|--------|------|

|                            |         | R        | MAPE | R    | MAPE | R      | MAPE |

|                            |         |          | (%)  |      | (%)  |        | (%)  |

| A #20                      | w/o opt | 0.99     | 5    | 0.99 | 5    | 0.99   | 4    |

| Area                       | w/ opt  | 0.95     | 34   | 0.95 | 18   | 0.96   | 11   |

| Power                      | w/o opt | 0.99     | 34   | 0.99 | 12   | 0.99   | 8    |

|                            | w/ opt  | 0.73     | 38   | 0.76 | 19   | 0.86   | 12   |

|                            | ·       |          |      |      |      |        |      |

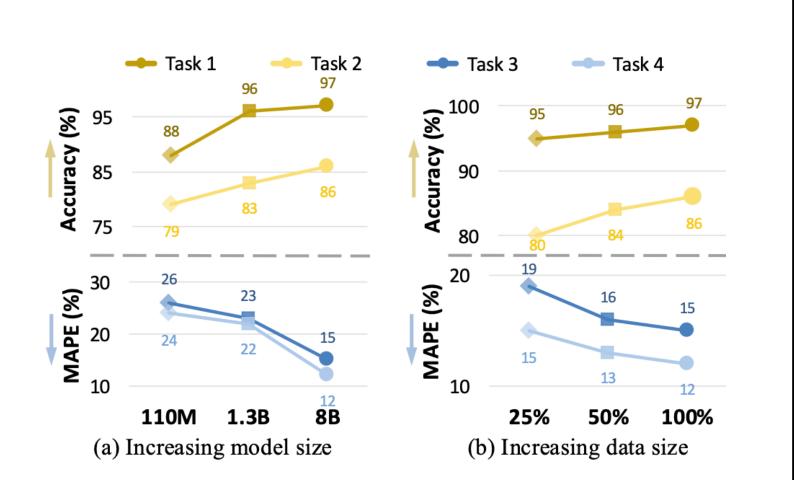

### ☐ Circuit Foundation Model Scaling Law

- Performance scaling up with model/data size

#### **Conclusion and Future Work**

☐ NetTAG: Graph-Only → LLM + Graph Fusion

☐ Future Work

- Integrate NetTAG into LLMs